# **AM2861 H-Bridge Brushed DC Motor Driver**

#### Features and Benefits

- 1) Operation Voltage Range: 4V to 33V

- 2) Lowest  $R_{DS (ON)}$ : HS +LS = 115m $\Omega$

- 3) 3A Continuous Current, 5A Peak Current

- 4) Over Temperature Protection

- 5) Over Current Protection

- 6) Low Standby Current < 2uA

- 7) Low Quiescent Current

- 8) SOP-8 Package For Small Size PCB Layout

#### Applications

- Robotics

- Al Home Appliances

- Robot Vacuum

- Electric Curtain

- Servo Motor

- Industrial Equipment

- Other Mechatronic Applications

- DC Brushed Motor Drive

# Description

AM2861 is a brushed DC motor driver IC, provides outside PWM pulse to control motor speed, and it drives current capability up to 3A continuous and 5A peak.

The device provides well protections for motor and device itself including internal functions for overcurrent and over temperature protection.

## Ordering Information

| Orderable Part Number | Package | Marking |

|-----------------------|---------|---------|

| AM2861                | SOP-8   | AM2861  |

# ■ Absolute Maximum Ratings (T<sub>A</sub>=25°C)

| Parameter                   | Symbol             | Limits    | Unit                    |

|-----------------------------|--------------------|-----------|-------------------------|

| Power Supply Voltage        | VCC                | 42        | V                       |

| Input IN_A and IN_B Voltage | V <sub>IN_X</sub>  | -0.3 to 6 | V                       |

| Peak Current                | lo <sub>peak</sub> | 5         | А                       |

| Operating Temperature Range | T <sub>opr</sub>   | -40~+125  | $^{\circ}\!\mathbb{C}$  |

| Storage Temperature Range   | T <sub>stg</sub>   | -40~+150  | $^{\circ}\! \mathbb{C}$ |

# ESD Ratings

|                                          |                                       | Value | Unit |

|------------------------------------------|---------------------------------------|-------|------|

| V Flortmostatio discharge                | Human-body model (HBM) <sup>(1)</sup> | ±8000 | V    |

| V <sub>ESD</sub> Electrostatic discharge | Machine model (MM) (1)                | ±400  | V    |

<sup>(1)</sup> The test method refers to JEDEC EIA/JESD22-A114-B.

# • Recommended Operating Conditions ( $T_A = 25^{\circ}C$ )

(Set the power supply voltage taking allowable dissipation into considering)

| Parameter                        | Symbol            | Min. | Тур. | Max.             | Unit |

|----------------------------------|-------------------|------|------|------------------|------|

| Power Supply Voltage             | VCC               | 4    |      | 33               | V    |

| Input IN_A and IN_B Voltage      | V <sub>IN_X</sub> | -0.3 |      | 6 <sup>(1)</sup> | V    |

| H-Bridge Output Current          | I <sub>OUT</sub>  |      |      | 3 <sup>(2)</sup> | А    |

| Externally Applied PWM Frequency | F <sub>IN_X</sub> |      |      | 30               | KHz  |

(1) Input signal voltage does not be higher than VCC voltage.

(2) Power dissipation and thermal limits must be observed

# ullet Electrical Characteristics ( Unless otherwise specified, $T_A$ = 25 $^{\circ}$ C, VCC=6V)

| Downwater                    | Parameter Symbol Limit |      |      | l l in | Conditions             |                                               |  |

|------------------------------|------------------------|------|------|--------|------------------------|-----------------------------------------------|--|

| Parameter                    | Symbol                 | Min. | Тур. | Max.   | Unit                   | Conditions                                    |  |

| Power Supply                 |                        |      |      |        |                        |                                               |  |

| Supply Current               | I <sub>cc</sub>        |      | 4    |        | mA                     | IN_A/B= L/H or H/L or H/H No load on OUT_A/B, |  |

| Standby Current              | $I_{STB}$              |      |      | 2      | uA                     | IN_A/B= L/L                                   |  |

| IN_X Inputs                  |                        |      |      |        |                        |                                               |  |

| Input H level Voltage        | $V_{\text{IN\_XH}}$    | 2.0  |      | 6      | V                      |                                               |  |

| Input L level Voltage        | $V_{IN_{XL}}$          | -0.3 |      | 0.7    | V                      |                                               |  |

| Input H level Current        | I <sub>IN_X</sub>      |      | 100  |        | μΑ                     | V <sub>CC</sub> = 6V, V <sub>IN</sub> = 3V    |  |

| Input Frequency              | F <sub>IN_X</sub>      |      |      | 30     | KHz                    |                                               |  |

| Input Pulldown Resistance    | R <sub>IN_X</sub>      |      | 30   |        | ΚΩ                     |                                               |  |

| H-Bridge FETs                |                        |      |      |        |                        |                                               |  |

| On-Resistance                | R <sub>DS(ON)</sub>    |      | 115  |        | mΩ                     | I <sub>O</sub> = 1A<br>Upper and Lower total  |  |

| On-Resistance                | $R_{DS(ON)}$           |      | 130  |        | mΩ                     | I <sub>O</sub> = 3A<br>Upper and Lower total  |  |

| Overcurrent Protection       |                        |      |      |        |                        |                                               |  |

| Overcurrent Trip Level       | I <sub>OCP</sub>       |      | 5    |        | А                      |                                               |  |

| Thermal Shutdown Protection  |                        |      | •    | •      | •                      | •                                             |  |

| Thermal Shutdown Temperature | $TSD_P$                |      | 160  |        | $^{\circ}\!\mathbb{C}$ | *1                                            |  |

| Thermal Shutdown Release     | $TSD_R$                |      | 105  |        | $^{\circ}\!\mathbb{C}$ | *1                                            |  |

<sup>\*1:</sup> It is design target, not to be measured at production test.

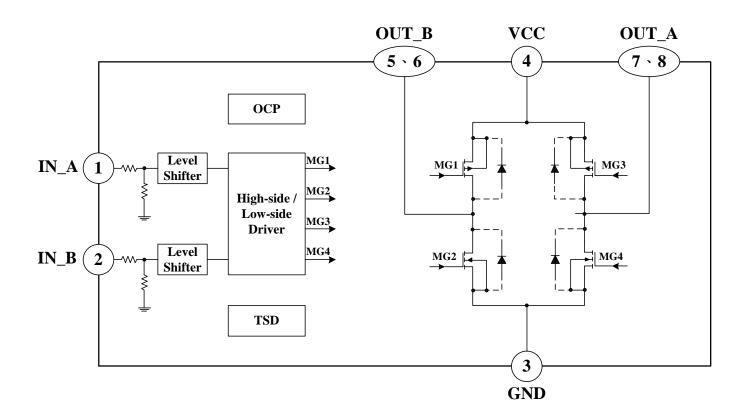

## Block Diagram

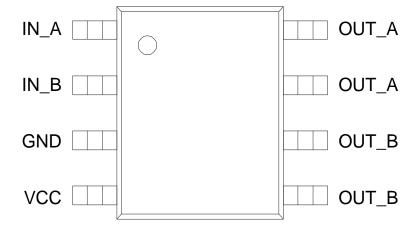

# Pin configuration SOP-8

# Pin Descriptions

| PIN No. | Pin Name | I/O | Description       |

|---------|----------|-----|-------------------|

| 1       | IN_A     | 1   | Logic Input A     |

| 2       | IN_B     | 1   | Logic Input B     |

| 3       | GND      | 1   | Ground Pin        |

| 4       | VCC      | I   | Power Supply      |

| 5       | OUT_B    | 0   | Output Terminal B |

| 6       | OUT_B    | 0   | Output Terminal B |

| 7       | OUT_A    | 0   | Output Terminal A |

| 8       | OUT_A    | 0   | Output Terminal A |

# Input Logic Descriptions

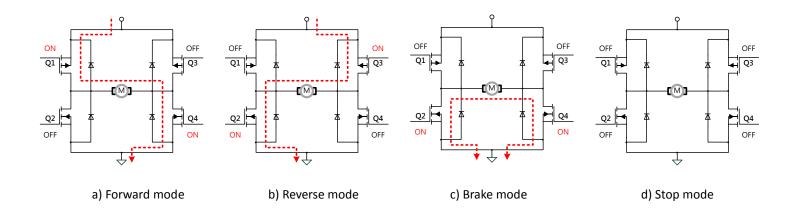

#### **Function Truth Table**

| IN_A | IN_B | OUT_A   | OUT_B   | Mode    |

|------|------|---------|---------|---------|

| L    | L    | High-Z* | High-Z* | Stop    |

| L    | Н    | L       | Н       | Reverse |

| Н    | L    | Н       | L       | Forward |

| Н    | Н    | L       | L       | Brake   |

Note\*: "High-Z" is the status that High-side MOSFETs and Low-side MOSFETs of H-Bridge are switched to "OFF".

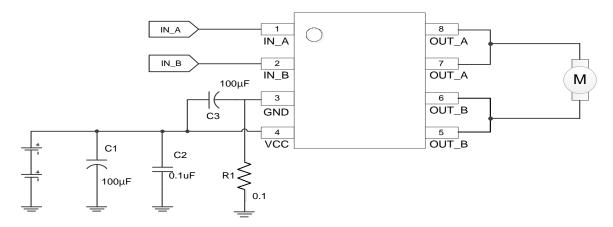

#### Application:

#### Circuit Descriptions

- 1. C1 \ C2: Power supply VCC pin capacitor:

- a. The capacitor can reduce the power spike when the motor is in motion, and prevent the IC from being damaged by the VCC peak voltage. They can stabilize the power supply voltage and reduce its ripples.

- b. The C1 capacitor can compensate power when motor starts running.

- c. The capacitor value (uF) determines the stability of the VCC during motor in motion. If the large voltage power or a heavier loading motor is used, then a larger capacitor would be needed.

- d. On the PCB configuration, the C1 \ C2 must be placed as close as possible to VCC pin.

- 2. If the C3 layout location is away from the VCC power line or the R1 resistor value is larger than 100mΩ, the C3 capacitors 100μF or is highly recommended to be placed in parallel with AM2861 VCC to GND; the capacitor layout location should be placed as close as practicable to AM2861. Please refer to above application circuit diagram, it is to suppress sampling resistor R1 ground noise to ensure MCU ADC detect sampling voltage precisely.

- 3. It's not allowed INA, INB input remain floating status, because there is a minor leakage current between P-N junction when temperature rising, the leakage current will go through internal pull- low resistor which causes INA or INB floating level abnormal pull high and output abnormal working.

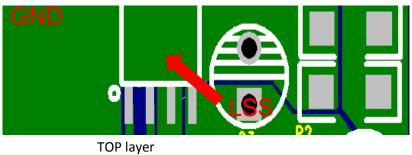

- 4. GND Pin (GND):

When current sense (sampling resistor) is used, to feedback sampling voltage to MCU precisely, please refer to following suggestion to get optimal performance:

In order to use PWM current control, a low-value resistor (R1) less than  $100m\Omega$  is placed between the GND pin for current sensing purposes. The ground-trace should be as short as possible. For low-value sense resistors, the ground-trace voltage drops in the PCB can be significant, and should be taken into account.

When selecting a value for the sense resistor, be sure not to exceed the maximum voltage on the GND pin of ±250 mV at maximum load. During over-current events, this rating may be exceeded for short durations.

The resistance of the sense resistor must be rated for high enough power.

#### Operating Mode Descriptions

a) Forward mode: When IN A=H, IN B=L, then OUT A=H, OUT B=L

b) Reverse mode: When IN\_A=L, IN\_B=H, then OUT\_A=L, OUT\_B=H

c) Brake mode: When IN\_A=IN\_B= H, then OUT\_A=OUT\_B=L

d) Stop mode: When IN\_A=IN\_B= L, then OUT\_A=OUT\_B=Hi-Z

# Protection Mechanisms Descriptions

#### 1) Over-current protection (OCP)

When the IC conducts a large current, 5A (Typ), the internal overcurrent protection will be triggered. The device enters protection mode and disables partial MOSFETs in the H-Bridge to avoid damaging IC and system. The device operation resumes when the current falls below safe range. If the overcurrent protection is still be triggered, the cycle repeats.

#### 2) Over-temperature protection

If the IC junction temperature exceeds  $160^{\circ}$ C (Typ.), the internal thermal shutdown protection will be triggered, and then partial FETs in the H-Bridge are disabled so that it will ensure the safety of customers' products. If the IC junction temperature falls to  $105^{\circ}$  C(Typ.), the IC resumes automatically.

### Layout Guidelines

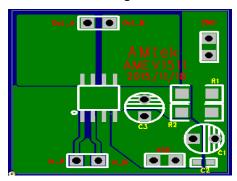

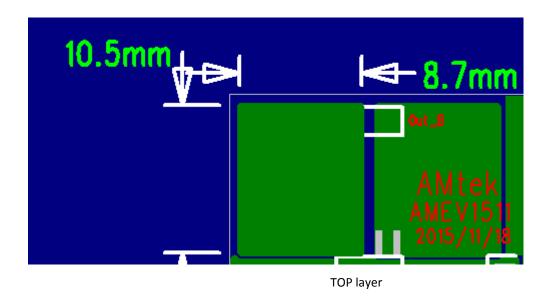

Layout Example

PCB Size 25x25 mm<sup>2</sup> \( \) single side

Top Layer

#### 2. Layout Consideration

The layout is very important when designing high current and high frequency switching converters. Layout will affect noise pickup. Correctly layout can realize a good design with less background noise. Make all the connections for the power components in the top layer with wide copper filled areas or polygons. In general, it is desirable to make proper use of GND planes and polygons for power distribution and heat dissipation.

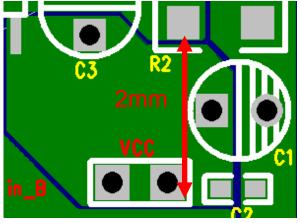

#### 3. Power trace

- 3.1 Power trace (VCC) should be as short as possible.

- 3.2 On the PCB configuration, the C1 and C2 must be mounted as close as possible to VCC pin in order to reduce EMI noise.

- 3.3 To ensure that power trace can conduct high current, the width of power trace should be wider than 2 mm.

#### 4. OUTPUT

- 4.1 OUT\_A and OUT\_B trace width need at least 2mm for high current going through.

- 4.2 For OUT\_A & OUT\_B thermal design consideration, it should be big one piece of copper (for example: 10.8mm x 5.1mm) without any gaps.

#### 5. GND

GND is a high-current path through the motor driver. The width of connecting metal trace should be as wide as possible.

AMtek semiconductors

Sep. 2022 V1.4

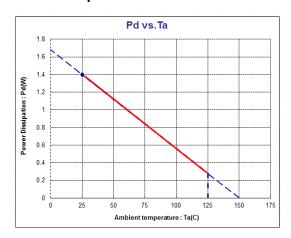

#### Thermal Information

| θја | junction-to-ambient thermal resistance     | 89.2°C/W          |

|-----|--------------------------------------------|-------------------|

| Ψjt | junction-to-top characterization parameter | 10.6°C <b>/</b> W |

Condition:

- a. FR4 PCB 25 x 25 mm<sup>2</sup>

- b. 1S1P-2 layers

- c. with 1 oz copper

#### Power Dissipation

# How to predict Tj in the environment of the actual PCB

- Step 1: Use the simulated  $\Psi$ jt value listed above.

- Step 2: Measure Tt value by using ~40 gauge thermocouple or thermo gun.

Tt: Temp. at top center of the package

Step 3: calculate power dissipation

$$P \cong (VCC - |V_{O\_Hi} - V_{O\_Li}|) \times I_{OUT} + VCC \times Icc$$

Step 4: Estimate Tj value

$$Tj = Tt + \Psi jt \times P$$

Step 5: Calculate Oja value of actual PCB

$$\theta ja = \frac{(Tj-Ta)}{P} = \ \frac{Tt+\Psi jt \ \times P - Ta}{P} = \frac{Tt-Ta}{P} + \ \Psi jt$$

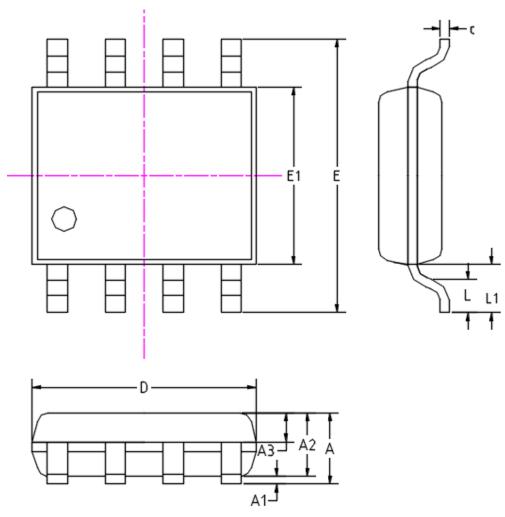

Packaging outline --- SOP-8

| SYMBOL | MILLIM    | 1ETERS | INC   | HES    |

|--------|-----------|--------|-------|--------|

|        | Min.      | Max.   | Min.  | Max.   |

| Α      |           | 1.75   | 1     | 0.069  |

| A1     | 0.10      | 0.25   | 0.004 | 0.010  |

| A2     | 1.25      | 1.65   | 0.049 | 0.065  |

| A3     | 0.50      | 0.70   | 0.020 | 0.028  |

| b      | 0.39      | 0.49   | 0.015 | 0.190  |

| С      | 0.10      | 0.25   | 0.004 | 0.010  |

| D      | 4.80      | 5.00   | 0.189 | 0.197  |

| E      | 5.90      | 6.10   | 0.232 | 0.240  |

| E1     | 3.80      | 4.00   | 0.150 | 0.157  |

| е      | 1.27 TYP. |        | 0.05  | TYP.   |

| L      | 0.45      | 1.00   | 0.018 | 0.039  |

| L1     | 1.10      | TYP    | 0.043 | 3 TYP. |

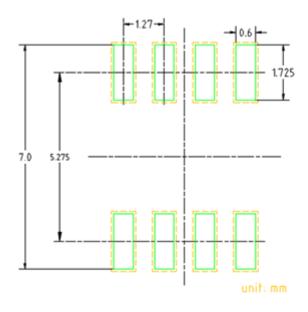

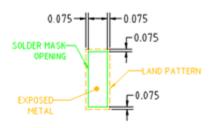

#### Land Pattern And Solder Mask

SOP-8 LAND PATTERN

Solder Mask Define

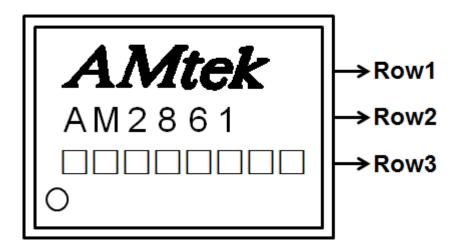

#### Marking Identification

Package Type: SOP8

Device: AM2861

#### NOTE:

Row1 : Logo

Row2 : Device Name

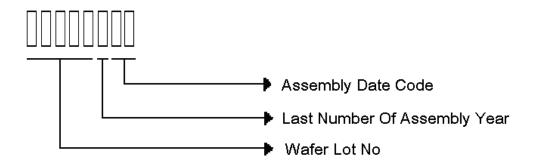

Row3 : Wafer Lot No use five codes + Assembly Year use one code + Assembly Week use two codes

Example: Wafer Lot No is EB168 + Year 2017 is H + Week 08 is 08, then mark "EB168H08"

The last code of assembly year, explanation as below: :

(Year: A=0,B=1,C=2,D=3,E=4,F=5,G=6,H=7,I=8,J=9. For example: year 2017=H)

# Revision History

| Date        | Revision | Changes                                                                        |

|-------------|----------|--------------------------------------------------------------------------------|

| 9.Oct.2018  | V1.0     | New release                                                                    |

| 13.Nov.2018 | V1.1     | P2. Operate voltage range change to 3.6 ~33V                                   |

|             |          | P3. OCP retry time chage to 0.5ms                                              |

|             |          | P8. Add layout Guideline                                                       |

| 3.Jun.2019  | V1.2     | P1. Add overcurrent protection                                                 |

|             |          | P3. Input low level range change to -0.3 ~ 0.7V                                |

|             |          | P4. Revise Block Diagram                                                       |

| 3.Nov.2020  | V1.3     | P2. Operate voltage range change to 4 ~33V                                     |

| 5.NOV.2020  | V1.5     | P3. Remove deglitch time and retry time                                        |

|             |          | P2. Operating Temperature Range change to $-40^{\circ}$ C $\sim 125^{\circ}$ C |

|             |          | Add ESD Rating                                                                 |

|             |          | P3. Add overcurrent Protection                                                 |

| 29.Sep.2022 | V1.4     | P10. Revise Power Dissipation                                                  |

|             |          | P11. POD update                                                                |

|             |          | P12. Add Land pattern and solder mask                                          |

|             |          | P14. Add Revision History                                                      |

#### Notice:

The information in this document is subject to change without notice. Please contact AMtek for current specifications.

Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating AMtek products into any application. AMtek will not assume any legal responsibility for any said applications.